#### CENTRE FOR DISTANCE EDUCATION ACHARYA NAGARJUNA UNIVERSITY :: NAGARJUNANAGAR – 522 510

M.Sc Physics (Second year)

Paper XI: Laboratory practical III: Electronics

- 1. Digital counters

- 2. Digital shift Registers

- 3. FET amplifier frequency response curve.

- 4. Astable multivibrator using 555 timer.

- 5 Op.Amp as inverting, non-inverting amplifier and, summing amplifier...

- 6. Wein bridge oscillator (op.Amp)

- 7. Colpitts Oscillator(Op.Amp)

- 8. Active filters (Op.Amp)

- 9. Assembly language programming of 8085 I

- 10. Assembly language pragramming of 8085 II

- 11. Assembly language programming of 8085 III

- 12. Assembly language pragramming of 8085 IV

# CENTRE FOR DISTANCE EDUCATION ACHARYA NAGARJUNA UNIVERSITY :: NAGARJUNANAGAR – 522 510

M.Sc Physics (Second year)

Paper XII: Laboratory practical IV: Solid State Physics

- 1. Dielectric constant of a ferroelectric material-curie temperature.

- 2. Specific heat of graphite variation with temperature.

- 3. Thermal expansion in the crystal –optical method.

- 4.Lattice dynamics-mono atomic and diatomic lattice.

- 5. Hall coefficient in semiconductors and density of charge carriers.

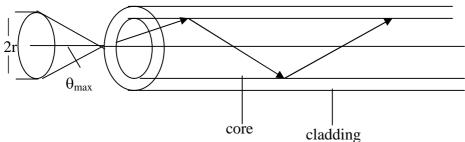

- 6. Fiber optics characteristics: Measurement of Numerical Aperture of mono/multi step/grade index optical fiber

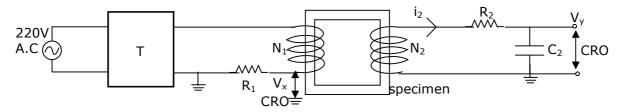

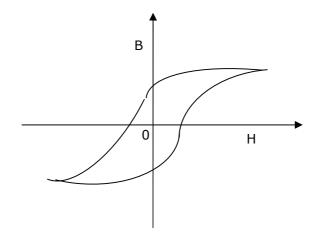

- 7. B H curve.

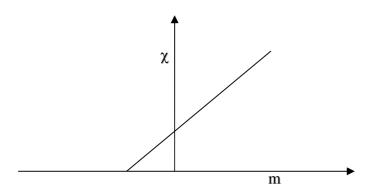

- 8. Magnetic susceptibility of a solution of paramagnetic salt-concentration variation (Quinckes method).

- 9.Band gap of a semiconductor-four probe method.

- 10.X-ray powder diffraction pattern-determination of lattice constants.

- 11. Electron spin resonance-determination of g factor for DPPH.

- 12. Dielectric constant of a (solid or) liquid at microwave frequency (3cm)

# **Contents**

#### **PRACTICAL - III**

Page Nos.

- 1. Digital counters

- 2. Digital shift Registers

- 3. FET amplifier frequency response curve.

- 4(a) A stable multivibrator using op. Amp 741

- 4(b)Astable multivibrator using 555 timer.

- 5 Op.Amp as inverting, non-inverting amplifier and, summing amplifier...

- 6. Wein bridge oscillator (op.Amp)

- 7. Colpitts Oscillator(Op.Amp)

- 8. Active filters (Op.Amp)

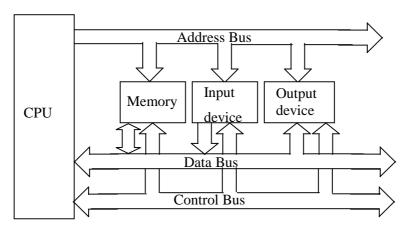

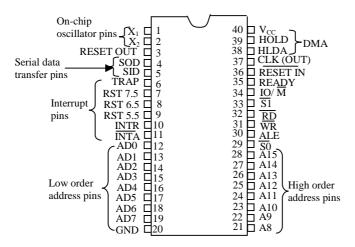

- 9. Intel 8085 microprocessor: Addressing modes

- 10. Intel 8085 microprocessor: Archetecture

- 11. Intel 8085 microprocessor:Instructions

- 12. Assembly language programming of 8085 I : Data Transfer

- 13. Assembly language pragramming of 8085 II : Logical group of instructions

- 14. Assembly language programming of 8085 III: Arithmetic program 1

- 15. Assembly language pragramming of 8085 IV: Arithmetic program 2

#### **PRACTICAL - IV**

- 1. Dielectric constant of a ferroelectric material-curie temperature.

- 2. Specific heat of graphite variation with temperature.

- 3. Thermal expansion in the crystal –optical method.

- 4. Lattice dynamics-mono atomic and diatomic lattice.

- 5. Hall coefficient in semiconductors and density of charge carriers.

- 6. Fiber optics characteristics: Measurement of Numerical Aperture

- 7. BH-curve.

- 8. Magnetic susceptibility (Quincke's method).

- 9. Band gap of a semiconductor

- 10. X-ray powder diffraction pattern-determination of a lattice constant.

- 11. Electron spin resonance-determination of g factor for DPPH.

- 12. Dielectric constant of a (solid or) liquid at microwave frequency (3cm)

Experiment No. 1

#### **DIGITAL COUNTERS**

1

**Aim**: To construct and study the working of (i) binary ripple counters, (ii) decade ripple counter

**Apparatus:** ICs:7476-three,7400-one,7405-one,7410-one;(2)IC power supply (5V ,1A Stabilized);(3) Pulser switch unit;(4)Lamp monitoring unit;(5)Clock generator;(6)Logical level switch

#### **Counters:**

A digital counter is a set of flip-flops (FFs) whose states change in response to pulses applied at the input to the counter. Thus, as its name implies, a counter is used to count pulses. A counter can also be used as a frequency divider to obtain waveforms with frequencies that are specific functions of the clock frequency. They are also used to perform the timing function as in digital watches, to create time delays, to produce non-sequential binary counts, to generate pulse trains, and to act as frequency counters, etc.

Counters may be <u>asynchronous</u> counters or <u>synchronous</u> counters. The term <u>asynchronous</u> refers to events that do not occur at the same time. Asynchronous counters are also called Ripple counters. The asynchronous counter has a disadvantage, in so far as the unwanted spikes are concerned. This limitation is overcome in parallel counters. Propagation delay is a major disadvantage in asynchronous counters because it limits the rate at which the counter can be clocked and creates decoding problem.

The term synchronous as applied to counter operation means that the counter is clocked such that each flip-flop in the counter is triggered at the same time.

#### **Asynchronous counters:**

In a asynchronous counter, the flip-flop output transition serves as a source of triggering other flip-flops. In other words, the CP inputs of all flip-flops are triggered not by the incoming pulses but rather by the transition that that occurs in other flip-flops. In this section, we present some asynchronous counters and explain their operation.

#### Four – Bit Asynchronous Binary Counter:

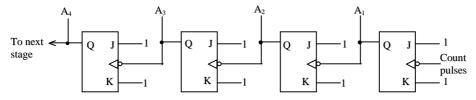

Four – Bit asynchronous binary counter consists of a series connection of complementing flip-flops, with the output of each flip-flop connected to the CP input of the next higher-order flip-flop. The flip-flop lading the least significant bit receives the incoming count pulses. The diagram of a 4 – bit binary ripple counter is shown in fig 1. All J and K inputs are equal to '1'. The small circle in the CP input indicates that the flip flop complements during a negative-going transition or when the output to which it is connected goes from 1 to 0.

Fig 1 – bit binary ripple counter

| Count sequence          | - C                       | anditions for complementing flip flops                           |

|-------------------------|---------------------------|------------------------------------------------------------------|

| $A_4$ $A_3$ $A_2$ $A_3$ |                           | onditions for complementing flip-flops                           |

| 0 0 0 0                 | Complement A <sub>1</sub> |                                                                  |

| 0 0 0 1                 | Complement A <sub>1</sub> | A <sub>1</sub> will go from 1 to 0 and Complement A <sub>2</sub> |

| 0 0 1 0                 | Complement A <sub>1</sub> |                                                                  |

| 0 0 1 1                 | Complement A <sub>1</sub> | A <sub>1</sub> will go from 1 to 0 and Complement A <sub>2</sub> |

|                         |                           | A <sub>2</sub> will go from 1 to 0 and Complement A <sub>3</sub> |

| 0 1 0 0                 | Complement A <sub>1</sub> |                                                                  |

| 0 1 0 1                 | Complement A <sub>1</sub> | A <sub>1</sub> will go from 1 to 0 and Complement A <sub>2</sub> |

| 0 1 1 0                 | Complement A <sub>1</sub> |                                                                  |

| 0 1 1 1                 | Complement A <sub>1</sub> | A <sub>1</sub> will go from 1 to 0 and Complement A <sub>2</sub> |

|                         | -                         | A <sub>2</sub> will go from 1 to 0 and Complement A <sub>3</sub> |

| 1 0 0 0                 | and so on                 | A <sub>3</sub> will go from 1 to 0 and Complement A <sub>4</sub> |

|                         |                           | •                                                                |

Table 1 Count sequence for a binary ripple counter

To understand the operation of the binary counter, refer to its count sequence given in Table 1. It is obvious that the lowest order bit  $A_1$  must be complemented with each count pulse. Every time  $A_1$  goes from 1 to 0, it complements  $A_2$ . Every time  $A_2$  goes from 1 to 0, it complements  $A_3$ , and so on. For example, take the transition from count 0111 to 1000. The arrows in the table emphasize the transition in this case.  $A_1$  is complemented with the count pulse. Since  $A_1$  goes from 1 to 0, it triggers  $A_2$  and complements it. As a result,  $A_2$  goes from 1 to 0, which in turn complements  $A_3$ .  $A_3$  now goes from 1 to 0, which complements  $A_4$ . The output transition of  $A_4$ , if connected to a next stage, will not trigger the next flip-flop, since it goes from 0 to 1. The flip-flops change are at a time in rapid success on, and the signal propagates through the counter in a ripple fashion. Hence asynchronous counters are sometimes called asynchronous counters.

# The 7493A Four – Bit binary counter:-

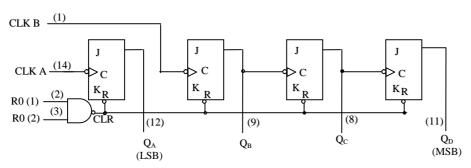

The 7493A is presented as an example of a specific integrated circuit asynchronous counter. As the logic diagram in fig 2 shows, this device actually consists of a single flip-flop and a three – bit asynchronous counter. This arrangement is for flexibility. It can be used as a divide – by-2 device using only the single flip-flop, or it can be used as a modulus – 8 counter using only the three-bit counter position. This device also provides gated reset inputs, RO(1) and RO(2). When both of these inputs are HIGH, the counter is RESET to the 0000 state by  $\overline{CLR}$ .

Fig 2 The 7493A four-bit binary counter logic diagram. (Pin numbers are in parentheses, and all J-K inputs are internally connected HIGH.

Additionally, the 7493A can be used as a four-bit modules-16 counter (counts 0 through 15) by connecting  $Q_A$  output to the CLK B input as shown in fig 2.

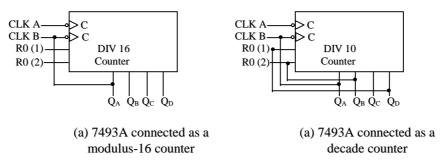

Fig 3 Two configurations of the 7493A asynchronous counter.

It can also be configured as a decade counter with asynchronous recycling by using the gated reset inputs for partial decoding of count  $10_{10}$ , as shown in fig 3.

#### **Asynchronous Decade Counters:**

Counters with ten states in their sequence are called <u>decade counter</u>. A decade counter with a count sequence of 0(0000) through 9(1001) is a BCD decade counter because its ten-state sequence is the BCD code. This type of counter is very useful in display applications in which BCD is required for conversion to a decimal readout.

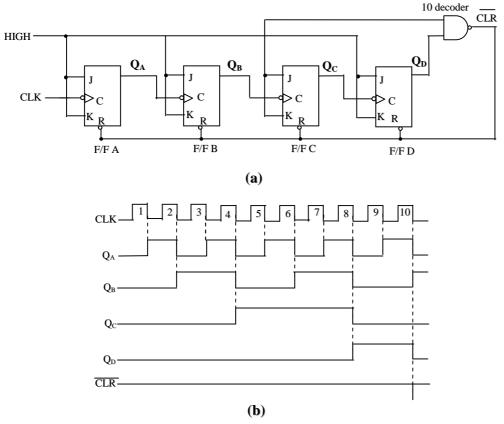

A decade counter requires four flip-flops. We will now take a four-bit asynchronous counter and modify its sequence in order to understand the principle of truncated counters. One method of achieving this recycling after the count of 9(1001) is to decode count  $10_{10}(1010)$  with a NAND gate and connect the output of the NAND gate to the clear (CLR) inputs of the flip-flops, as shown in fig 4.

Fig 4 An asynchronously clocked decade counter with asynchronous recycling.

Notice that only  $Q_B$  and  $Q_D$  are connected to the NAND gate inputs. This is an example of partial decoding, in which the two unique states ( $Q_B = 1$  and  $Q_D = 0$ ) are sufficient to decode the count of  $10_{10}$  because none of the other states (0 through 9) have both  $Q_B$  and  $Q_D$  HIGH at the same time. When the counter goes into count  $10_{10}(1010)$ , the decoding gate output goes LOW and asynchronously RESETS all of the flip-flops.

The resulting timing diagrams is shown in fig.4 Notice that there is a glitch on the  $Q_B$  wave form. The reason for this glitch is that  $Q_B$  must first go HIGH before the count of  $10_{10}$  can be decoded. Not until several nano seconds after the counter goes to the count of  $10_{10}$  does the output of the decoding gate go LOW. Thus, the counter is in the 1010 state for a short time before it is RESET back to 0000, thus producing the glitch on  $Q_B$ .

#### **Synchronous Counters:**

Synchronous counters are distinguished from ripple counters in that clock pulses are applied to the CP inputs of all flip-flops. The common pulse triggers all the filp-flops simultaneously, rather than one at a time in succession as in a ripple counter. The decision whether a flip-flop is to be complemented or not is determined from the values of the J and K inputs at the time of the pulse. If J = K = 0, the flip-flop remains unchanged. If J = K = 1, the flip-flop complements. In this section, we present some typical MSI synchronous counters and explain their operation.

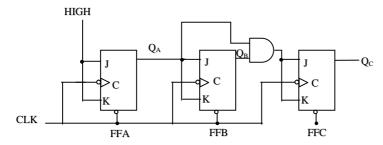

#### Three - Bit Synchronous Binary counter:

Three bit synchronous binary counter is shown in fig 5 and its timing diagram in (fig 6). An understanding of this counter can be achieved by a careful examination of its sequence of states as shown in Table 2.

Fig 5 A three – bit synchronous binary counter.

Fig 6) Timing diagram for the counter of figure.

First , let us look at  $Q_A$ . Notice that  $Q_A$  changes on each clock pulse as we progress from its original state to its final state and then back to its original state. To produce this operation, FFA must be held in the toggle mode by constant HIGH on its J and K inputs. Now let us see what  $Q_B$  does. Notice that it goes to the opposite state following each time  $Q_A$  is a 1. This occurs at  $CLK_2$ ,  $CLK_4$ ,  $CLK_6$  and  $CLK_8$ .  $CLK_8$  causes the counter to recycle. To produce this operation,  $Q_A$  is connected to the J and K inputs of FFB. When  $Q_A$  is a 1 and a clock pulse occurs. FFB is the toggle mode and will change state. The other times when  $Q_A$  is a 0, FFB is in the no-change mode and remains in its present state.

| Cleals Dules | 0       |                | 0              |

|--------------|---------|----------------|----------------|

| Clock Pulse  | $Q_{C}$ | Q <sub>B</sub> | Q <sub>A</sub> |

| 0            | 0       | 0              | 0              |

| 1            | 0       | 0              | 1              |

| 2            | 0       | 1              | 0              |

| 3            | 0       | 1              | 1              |

| 4            | 1       | 0              | 0              |

| 5            | 1       | 0              | 1              |

| 6            | 1       | 1              | 0              |

| 7            | 1       | 1              | 1              |

| •            |         |                |                |

Table 2 State sequence for a three-stage binary counter.

Next, let us see how FFC is made to change at the proper times according to the binary sequence. Notice that both times  $Q_C$  changes state, it is preceded by the unique condition of both  $Q_A$  and  $Q_B$  being HIGH. This condition is detected by the AND gate and applied to the J and K inputs of FFC. Whenever both  $Q_A$  and  $Q_B$  being HIGH, the output of the AND gate makes the J and K inputs of FFC HIGH, and FFC toggle on the following clock pulse. At all other times, the J and K inputs of FFC are held LOW by the AND gate output, and FFC does not change state.

#### **Experimental Procedure:**

a) Asynchronous Binary up Counter:

Wire the four-bit ripple counter as shown in fig.1 using two IC7476s. Monitor the logic levels at D,C,B,A using the lamp monitoring units. Feed the counter with the pulser switch. Tie up all clear inputs and connect to pulser switch. Clear the FFs to read O by momentarily pressing the pulser switch. Apply sixteen pulses one by one and observe the D,C,B,A outputs and fill in the Table3.

| Table 3 Asynchronous Binary U | p C | ounter |

|-------------------------------|-----|--------|

|-------------------------------|-----|--------|

| INPUT | D | С | В | A |   |

|-------|---|---|---|---|---|

| 0     | 0 | 0 | 0 | 0 |   |

| 1     |   |   |   |   |   |

| 2     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| -     |   |   |   |   |   |

| _     |   | _ |   |   |   |

| _     |   |   |   |   |   |

| -     |   |   |   |   |   |

| 16    | 0 | 0 | 0 | 0 | 0 |

Apply 1kHz square wave from the clock generator to the input and observe the output waves at D,C,B,A using a dual trace CRO

- b) Asynchronous Binary down Counter:

- 1. wire the circuit using two IC 7476s

- 2.Clear the counter . the D,C,B,A outputs show logic level 1.

- 3.Enter sixteen clock pulses using PSI and observe the outputs after each input pulse. Enter your results in a table similar to table 7.

- 4. Observe the relation between the input and output waveforms using a dual trace oscilloscope . Feed the counter with 1kHz signal from the clock generator.

# c) Decade Ripple Counter:

Wire the decade ripple counter circuit as shown in fig 4 using two IC7476s and a NAND gate (IC7400). Feed the counter units with the pulser switch(PSI) and monitor the outputs using lamp monitors units. Enter ten pulses one by one and note the output levels after each input pulse. Record your observations in a tabular form.

# d)Modulo -3 Counter:

Two FFs are required to construct a modulo-3 counter as shown in fig wire the circuit using IC7476.Monitor B and A outputs using the lamp monitoring unit. Feed the counter with the pulser switch. Verify the count sequence .

## (e)Modulo –8 synchronous binary counter:

Wire the circuit shown as in fig 5 using two IC7476s and one IC7410. Feed the input with positive pulses and monitor C,B,A outputs with the help of the lamp monitoring unit.

# **Precautions:**

1. Verify the proper functioning of individual logic components used in the circuit before using them in the circuit

**Results:** The working the logic circuit for the decade counter is is as per the truth table.

Experiment No. 2

#### **SHIFT REGISTERS**

1

Aim: To study the working of four bit shift register

**Apparatus**: Two I C 7476, One I C 7405 Or 7400, Power supply, Bread board

# **Shift Register:**

Shift registers are very important in applications involving the storage and transfer of data in digital system. A register, in general, is used solely for storing and shifting data (1s and 0s) entered into it from all external sources and <u>possesses</u> no characteristic internal sequence of states. The storage capability of a register is one of its two basic functional characteristics and makes it an important type of memory device.

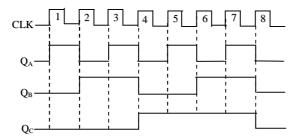

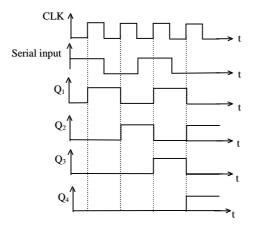

Figure 1 : Basic data movement in registers.

Registers are commonly used for the temporary storage of data within a digital system. The shift capability of a register permits the movement of data from stage to stage within the register or into or out of the register upon application of clock pulses.

Fig 1 shows symbolically the types of data movement in shift register operations. The block represents any arbitrary four-bit register, and the arrow indicates the direction and type of data movement.

M.Sc.Physics 2 Shift registers

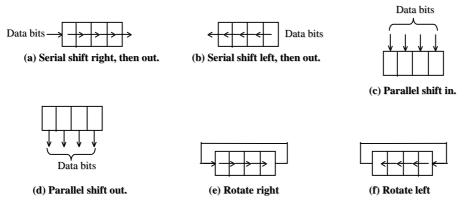

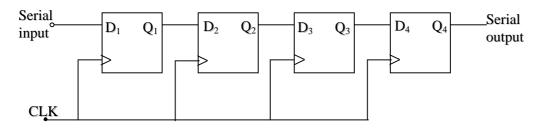

## Serial In – Serial out Shift Register:

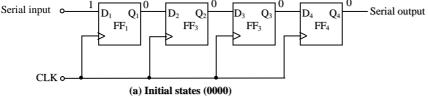

This type of shift register accepts data serially, i.e. one bit at a time, and also outputs data serially. The logic diagram of a 4 – bit serial – in, serial – out, shift register is shown in fig 2. with four stages, i.e., four flip –flops, the register can store up to four bits of data.

Figure 2 – bit serial – in, serial – out, shift register

Serial data is applied at the D input of the first Flip-Flop (FF). The Q output of the first FF is connected to the D input of the second FF, the Q output of the second FF is connected to the D input of the third FF and the Q output of the third FF is connected to the D input of the fourth FF. The data is outputted from the Q terminal of the last FF.

When serial data is transferred into a register, each new bit is clocked into the first FF at the positive – going edge of each clock pulse. The bit that was previously stored by the first FF is transferred to the second FF. The bit that was stored by the second FF is transferred to the third FF, and so on. The bit that was stored by the last FF is shifted out.

Fig 3 and table 1 illustrate this process to store the data bits 0101 in the register. Initially all the FFs are reset, i.e.,  $Q_1 = 0$ ,  $Q_2 = 0$ ,  $Q_3 = 0$  and  $Q_4 = 0$ .

The right most bit '1' is applied at the  $D_1$  input of  $FF_1$ . At the positive – going edge of the first clock pulse, this '1' is shifted into  $FF_1$  and all other FFs store their respective bits at the D inputs. Therefore,  $Q_1 = 1$ ,  $Q_2 = 0$ ,  $Q_3 = 0$  and  $Q_4 = 0$ , after the first clock pulse.

Then a '0' is applied at the  $D_1$  input of  $FF_1$ . At the positive – going edge of the second clock pulse, this '0' is shifted to  $Q_1$  of  $FF_1$  and the D inputs of all other FFs are also shifted to their respective outputs. Therefore  $Q_1 = 0$ ,  $Q_2 = 1$ ,  $Q_3 = 0$  and  $Q_4 = 0$ , after the second clock pulse.

Fig3 Loading of the 4 – bit serial – in, serial – out, shift register

Then a '1' is applied at the  $D_1$  input of  $FF_1$ . At the positive – going edge of the third clock pulse, this '1' is shifted into  $Q_1$  of  $FF_1$  and the D inputs of all other FFs are also shifted to their respective outputs. Therefore,  $Q_1 = 1$ ,  $Q_2 = 0$ ,  $Q_3 = 1$  and  $Q_4 = 0$ , after the third clock pulse.

Then a '0' is applied at the  $D_1$  input of  $FF_1$ . At the positive – going edge of the fourth clock pulse, this '0' is shifted into  $Q_1$  of  $FF_1$  and the D inputs of all other FFs are also shifted to their respective outputs. Therefore,  $Q_1 = 0$ ,  $Q_2 = 1$ ,  $Q_3 = 0$  and  $Q_4 = 1$ , after the third clock pulse, this '0' is shifted to  $Q_1$  of  $FF_1$  and the D inputs of all other  $FF_S$  are also shifted to their respective outputs. Therefore,

| After clock pulse | Serial input | $\mathbf{Q}_1$ | $Q_2$ | $Q_3$ | $Q_4$ | _              |

|-------------------|--------------|----------------|-------|-------|-------|----------------|

| 0                 | 1 _          | 0              | 0     | 0 <   | 0     | Initial states |

| 1                 | 0            | 1              | 0     | 0     | 0     |                |

| 2                 | 1            | 0              | 1     | 0     | 0     |                |

| 3                 | 0            | 1              | 0     | 1     | 0     |                |

| 4                 |              | 0              | 1     | 0     | 1     |                |

Table 1 Shifting in the data 0101 serially.

M.Sc.Physics 4 Shift registers

$Q_1 = 0$ ,  $Q_2 = 1$ ,  $Q_3 = 0$  and  $Q_4 = 1$ , after the fourth clock pulse.

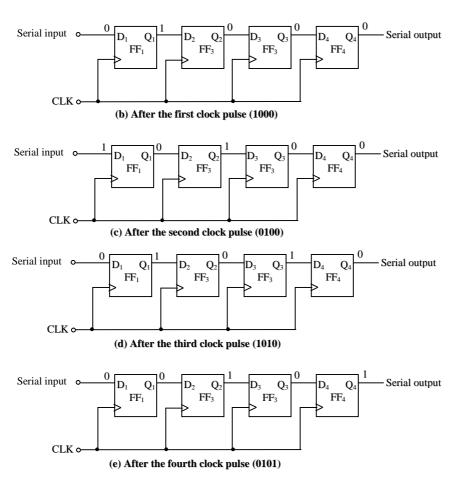

This completes the serial entry of 0101 into the 4-bit register fig 4 shows the timing diagram of the loading of serial input 0101 into the 4-bit serial-in, serial-out, shift register.

Fig 4 Timing diagram showing the loading of the serial input 0101 into the 4 – bit Serial-in, Serial-out, shift register.

The shifting out of the stored data 0101 serially from the register is illustrated in table 2. It requires four clock pulses to shift out the 4-bit stored data.

| After clock pulse | Serial input | $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$          |

|-------------------|--------------|-------|-------|-------|----------------|

| 0                 | 0 _          | 0     | 1     | 0 <   | 1              |

| 1                 | 0            | 0     | 0     | 1     | <sub>2</sub> 0 |

| 2                 | 0            | 0     | 0     | 0     | 1              |

| 3                 | 0            | , 0   | 0     | 0     | 0              |

| 4                 | _            | 0     | 0     | 0     | 0              |

|                   |              |       |       |       |                |

Table 2 Shifting in the data 0101 serially.

#### Serial In, Parallel – out Shift Register:

In this type of register, the data bits are entered into the register serially, but the data stored in the register is shifted out in parallel form. Fig 5 shows the logic diagram and the logic symbol of a 4-bit serial – in, parallel – out shift register.

Once the data bits are stored, each bit appears on its respective output line and all bits are available simultaneously, rather than on a bit-by-bit basis as with the serial output. The serial – in, parallel-out, shift register can be used as a serial-in, serial-out, shift register, if the output is taken from the Q terminal of the last FF.

5

Fig (5) 4 – bit serial - in, parallel - out, shift register.

#### Parallel In, Serial – Out Shift Register:

In parallel – in, serial-out, shift register, the data bits are entered simultaneously into their respective stages on parallel lines, rather than on a bit-by-bit basis on one line as with serial data inputs, but the data bits are transferred out of the register serially, i.e., on a bit-by-bit basis over a single line.

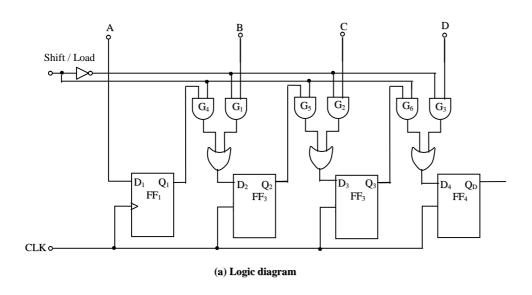

Fig 6 illustrates a 4-bit parallel-in, serial out, shift register using D flip-flops. There are four data lines A, B, C and D through which the data is entered into the register in parallel form. The signal shift / load allows (a) the data to be entered in parallel form into the register and (b) the data to be shifted out serially from terminal  $Q_4$ .

When Shift / Load line is high, gates  $G_1$ ,  $G_2$  and  $G_3$  are disabled, but gates  $G_4$ ,  $G_5$  and  $G_6$  are enabled allowing the data bits to shift – right from one stage to the next. When Shift / Load line is low, gates  $G_4$ ,  $G_5$  and  $G_6$  are disabled, whereas gates  $G_1$ ,  $G_2$  and  $G_3$  are enabled allowing the data input to appear at the D inputs of the respective flip-flops. When a clock pulse is applied, these data bits are shifted to the Q output terminals of the flip-flops and therefore, data is inputted in one step. The OR gate allows either the normal shifting operation or the parallel data entry depending on which AND gates are enabled by the level on the Shift / Load input.

Fig 6 A 4-bit parallel, serial – out, shift register.

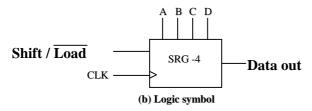

# Parallel In, Parallel – out Shift Register:

<u>Figure 7 Logic diagram of a 4 – bit parallel – in, parallel – out, shift register</u>

In a parallel – in, parallel – out, shift register, the data is entered into the register in parallel form, and also the data is taken out of the register in parallel form. Immediately following the simultaneous entry of all data bits, the bits appear on the parallel outputs.

7

Fig 7 shows a 4-bit parallel-in, parallel-out, shift register using D Flip-Flops. Data is applied to the D input terminals of the flip-flops. When a clock pulse is applied, at the positive going edge of that pulse, the D inputs are shifted in to the Q outputs of the Flip-Flops. The register now stores the data. The stored data is available instantaneously for shifting out in parallel form.

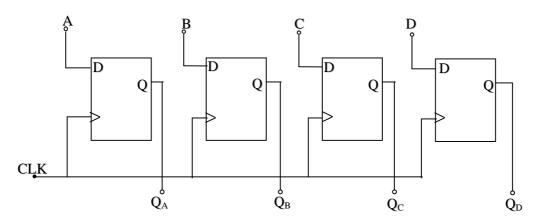

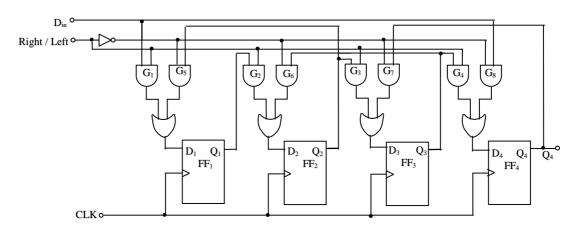

#### **Bi-directional Shifter:**

A bidirectional shift register is one in which the data bits can be shifted from left to right or from right to left.

Fig 8 shows the logic diagram of a 4-bit serial-in, serial-out, bi-directional shift register. Right/Left is the mode signal.

Fig 8 Logic diagram of a 4 – bit bi-directional shift register.

When Right /  $\overline{\text{Left}}$  is a 1, the logic circuit works as a shift-right shift register. When Right /  $\overline{\text{Left}}$  is a 0, it works as a shift – left register. The bidirectional operation is achieved by using the mode signal and two AND gates and one OR gate for each stage as shown in fig 8.

A HIGH on the Right /Left control input enables the AND gates  $G_1$ ,  $G_2$ ,  $G_3$  and  $G_4$  and disables the AND gates  $G_5$ ,  $G_6$ ,  $G_7$  and  $G_8$  and the state of Q output of each FF is passed through the gate to the D input of the following FF. When a clock pulse occurs, the data bits are then effectively shifted one place to the right. A low on the Right / $\overline{\text{Left}}$  control input enables the AND gates  $G_5$ ,  $G_6$ ,  $G_7$  and  $G_8$  and disables the AND gates  $G_1$ ,  $G_2$ ,  $G_3$  and  $G_4$  and the Q output of each

M.Sc.Physics 8 Shift registers

Flip-Flop is passed to the D input of the preceding FF. When a clock pulse occurs, the data bits are then effectively shifted one place to the left. Hence, the circuit works as a bidirectional shift register.

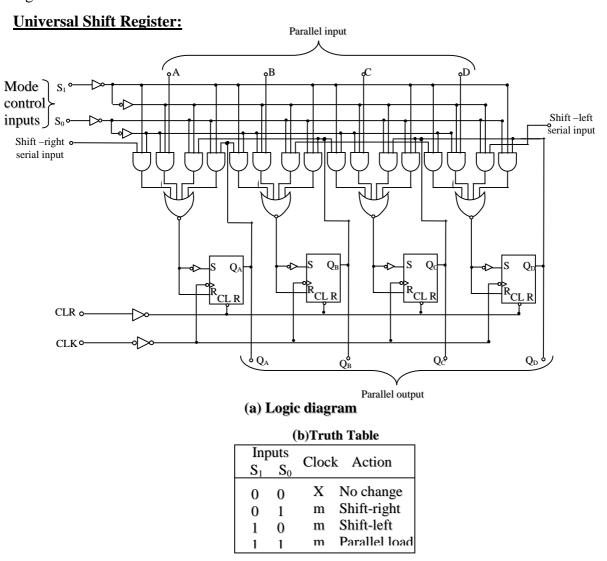

Fig 9 The 74194 4-bit universal shift register.

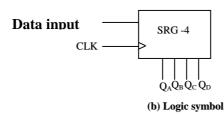

A universal shift Register is a bidirectional register, whose input can be either in serial form or in parallel form and whose output also can be either in serial form or in parallel form.

Fig 9 shows the logic diagrams of the 74194 4-bit universal shift register. The output of each flip-flop is routed through AOI logic to the stage on its right and to the stage on its left. The mode control inputs,  $S_0$  and  $S_1$  are used to enable the left-to-right connections. When it is desired to shift-right, and the right-to-left connections. When it is desired to Shift-Left.

The truth table (tabl3 3) shows that no shifting occurs when  $S_0$  and  $S_1$  are both LOW or both HIGH. When  $S_0 = S_1 = 0$ , there is no change in the contents of the register, and when  $S_0 = S_1 = 1$ , the parallel input data A, B, C and D are loaded into the register on the rising edge of the clock pulse. The combination  $S_0 = S_1 = 0$  is said to inhibit the loading of serial or parallel data, since the register contents cannot change under that condition. The register has an asynchronous active – LOW clear input, which can be used to reset all the flip-flops irrespective of the clock and any serial or parallel inputs.

#### Procedure:

Serial in – serial out shift register:

Using two 7476 Ics form 4 D-Flip flops and connect them as shown in Fig 2. to form a serial in serial out 4-bit shift register. Clear all the outputs by entering the reset pulse. All the outputs show level 0. Feed the clock input with the pulser switch `and monitor the logic levels of the output Q3 using the lamp monitoring unit. The J input of the flip – flop (FF0) is connected to the logic switch to provide information bits. Verify the truth table following the method described in theory.

#### Serial in parallel out shift register:

Using two 7476 Ics form 4 D-Flip flops and connect them as shown in Fig 5. to form a serial in parallel out 4-bit shift register. Clear all the outputs by entering the reset pulse. All the outputs show level 0. Feed the clock input with the pulser switch `and monitor the logic levels of the outputs Q0,Q1,Q2 and Q3 using the lamp monitoring unit. The J input of the flip – flop (FF0) is connected to the logic switch to provide information bits. Verify the truth table following the method described in theory.

#### Parallel in serial out shift register:

Using two 7476 Ics form 4 D-Flip flops and connect them as shown in Fig 7. to form a parallel in serial out 4-bit shift register. Clear all the outputs by entering the reset pulse. All the outputs show level 0. Feed the clock input with the pulser switch `and monitor the logic levels of the output Q3 using the lamp monitoring unit. Each of the inputs of the flip – flops A,B,C and D are preset with one bit data by connecting them to logic switches to provide information bits. Verify the truth table following the method described in theory.

## Parallel in- parallel out shift register:

Using two 7476 ICs form 4 D-Flip flops and connect them as shown in Fig 7. to form a parallel in serial out 4-bit shift register. Clear all the outputs by entering the reset pulse. All the outputs show level 0. Feed the clock input with the pulser switch `and monitor the logic levels of the outputs Q0,Q1,Q2 and Q3 using the lamp monitoring unit. Each of the inputs of the flip – flops A,B,C and D are preset with one bit data by connecting them to logic switches to provide information bits. Verify the truth table following the method described in theory.

#### Bi directional shift register:

Using two 7476 Ics form 4 D-Flip flops .Using one AND gate IC and two OR gate Ics connect the circuit as shown in Fig 8. to form a 4-bit bi directional shift register. Clear all the outputs by entering the reset pulse. All the outputs show level 0. Feed the clock input with the pulser switch `and monitor the logic levels of the output Q3 using the lamp monitoring unit. The D in input is connected to the logic switch to provide information bits. Verify the truth table following the method described in theory.

**Universal shift register**: Using a 74194 IC connect various logics to various pins as shown in fig 9. Using S0 and S1 controls and using the method given in theory test the various modes of operation of the Universal shift register and verify the truth table in each mode.

#### **Precautions:**

- 1. Avoid the loose contacts

- 2. Check proper working of the individual ICs before use

- 3. Make the perfect contact in breadboard

- 4. See that all ground points have common ground

- 5. Use different color wires for clear identification of various signals

**Result:** The circuits are assembled properly and the results are as per truth tables.

#### Experiment No. 3

# R-C coupled Single stage Common source FET amplifier

1

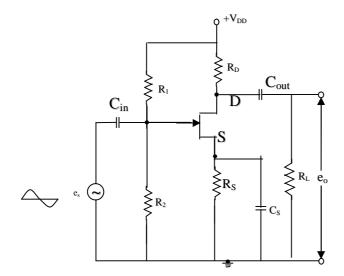

**Aim**: -To construct an RC coupled amp (FET version) and study its frequency response with and with out feedback.

**Apparatus**: - Field Effect Transistor BFW 10, resistances  $33k\Omega$ ,  $2.2k\Omega$ ,  $1k\Omega$ ,  $10k\Omega$ , Capacitances  $.2\mu$ f,  $2\mu$ f,  $50\mu$ f/65V, Signal generator, DC Power supply

#### Theory: -

An amplifier is a device by which one parameter like voltage, current or power of the given signal at input circuit can be increased and obtained at the output terminals by proper selection of the operating point of the transistor. There are several types of classifications of amplifiers basing on

1. Purpose: (Voltage amplifier, current amplifier. Power amplifier)

2. Coupling circuit: RC coupled, Inductance coupled, Transformer coupled

3. Operating point (Class A, Class B, Class C, Class AB)

In order to have very high amplification, we have to use multistage amplifiers. Here we take a single stage amplifier and study its performance. If a fraction of the output (current or voltage) is taken and fed to the input of transistor along with the input it is called feedback amplifier.

RC coupled amplifier can also be formed using Bi junction transistors and Field effect transistors. RC coupled amplifier based on BJT was covered already in the first year course. Here we construct an RC coupled amplifier based on FET and study its performance. The static characteristics of FET BFW 10 was studied in the first year course. We reproduce here some useful information about FETs

FET is a three terminal device. FET's can be characterized in two main categories like JFET(Junction Field Effect Transistor) and MOSFET(Metal Oxide Field semiconductor). Here we study the JFET characteristics. JFET's are further of two types n-channel type and p-channel type.

#### Main feature of JFET:-

- 1. It is a uni polar three terminal device, which solely depends on the conduction of either of electrons or holes.

- 2. In the operation of this the electric field established by the charges controls the conduction; hence the name Field Effect Transistor.

- 3. Field Effect Transistor is an voltage control device where as BJT is a current control device. The output current in the BJT is controlled by the input current level where as the output current in FET is controlled by the applied voltage in the input circuit.

- 4. There are two types of BJT i.e p-n-p and n-p-n. Similarly FET is of two types p-channel FET and n-channel FET.

- 5. Gate-source junction is generally reverse biased and gate drain junction is forward biased.

- 6. The effective channel width, which allows current flow, is controlled by reverse biasing the gate source junction, which changes the width of the space charge in the channel.

- 7. The reverse bias voltage given to gate- source junction, which just prevents the current flow from the source to drain is called "pinch off voltage".

- 8. The reverse biasing effect of the gate will be more at the drain end. As drain current is increased by increasing the drain voltage the reverse bias voltage appearing at the drain end (gate drain end) at some value of V<sub>a</sub> this exceeds the reverse breakdown value. Then an avalanche current will flow which is very large This is called breakdown region.

#### Parameters of FET:-

1. Dynamic Drain resistance (r<sub>d</sub>):- Dynamic drain resistance at an operating point is defined as the ratio of small change in drain voltage to the corresponding change in the drain current, when the gate voltage is kept constant.

$$r_{d} = \left(\Delta V_{DS}\right)/\left(\Delta \ I_{D}\right) \quad V_{GS} \ being \ constant.$$

The typical value of  $r_{d}$  is  $400\Omega(ohms)$ .

- 2. Mutual Conductance or Trans conductance  $(g_m)$ :- The trans- conductance at an operating point is defined as the ratio of a small change in drain current to the corresponding change in gate voltage when drain voltage is kept constant.  $g_m = (\Delta I_D) / (\Delta V_{GS})$  when  $V_{DS}$  is constant. Typical value of  $g_m$  is  $250\mu s$  (micro siemen).

- 3. Amplification Factor (μ):- Amplification factor is defined as the ratio of small change in drain voltage to the corresponding change in gate voltage when drain current is kept constant.

$\mu = (\Delta V_{DS}) / (\Delta V_{GS})$  when I is constant.

$\mu$  being the ratio of two voltages it has no units. Typical value of amplification factor of FET is around 10. The above parameters are related by

$$\mu = (r_d) \times g_m$$

The drain and the source terminals are taken from n-channel and gate terminal is taken from p type material.

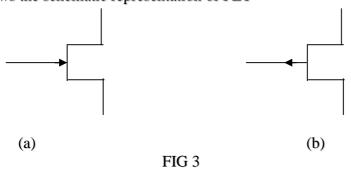

#### **Schematic representation:-**

Fig 3shows the schematic representation of FET

The arrow mark on the gate terminal indicates the direction in which gate current flows when gate junction is forward biased. For n-channel FET arrow is shown into the gate. For p- channel FET arrow is away from gate.

**Source:**- It is the terminal through majority charge carriers enter the bar.

**Drain**:- It is the terminal through which majority charge carriers leave the bar.

**Gate**:- It is the terminal which analogous to base terminal in BJT(Bipolar Junction Transistor) And controls the flow of charge carriers.

**Channel**:- The region between the source and drain through which majority charge carriers move. The width of this is adjustable by controlling the space charge region in it.

Distinction between BJT and FET amplifiers:

BJT is a Bipolar Device. FET is a Unipolar device.

In BJT amplifiers input junction is forward biased. In FETs it is reverse biased.

BJT is a current controlled device. FET is a field controlled device.

Input current of BJT will be in micro amperes. In FETs it will be in nano to pico amperes.

Input resistance of BJT is about 1kohm .For FET it is about 1 megaohm.

The gain of BJTs is high. Gain of FETs is small.

As the input resistance of FET is high in FET amplifiers to obtain same low frequency response ,it is sufficient if we use very small coupling capacitors when compared to the values coupling capacitors used in BJT amplifiers.

The frequency response of FETS is poor when compared to BJTs. However the technology is being improved to enhance frequency response and gain.

The characteristics of FET are more non linear when compared to BJT characteristics. Hence FET amplifiers produce more distortion in the output signal.

The amplitude of input signal can be larger in FET amplifiers when compared to BJT amplifiers.

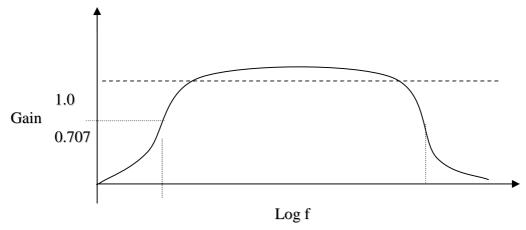

In the case of RC coupled amplifier a sinusoidal signal of about 30mV is given and output voltage is measured. The voltage amplification ( $A_v = V_{out}/V_{in}$ ) is calculated at different frequencies and plotted against frequency .

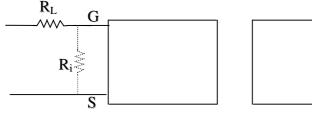

Fig 1 A single stage R-C coupled amplifier.

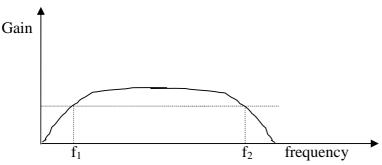

At low frequencies the amplification increases with increase of frequency and at high frequencies it falls with the increase of frequency. In the midband region gain remains as constant. The circuit diagram is given below (FIG 1). The frequency response curve is shown in fig 2

Normalized gain – frequency response curve

The behavior can be understood as follows. FIG2

Low frequency region: The reactance of coupling capacitor is quite high( $1/\omega C$ ) at low frequencies and thus the output decreases with the decrease of frequency in low frequency region. Further,  $C_S$  cannot effectively shunt to source resistance  $R_S$ . These are the two reasons that cause the fall in amplification in the low frequency region.

High frequency region: At high frequencies, the reactance of coupling capacitors is very small and they do not offer resistance. If there is a second stage this increases the loading effect and thus decreases the gain. Further, capacitive reactance of Gate source junction at high frequencies becomes low, which increases the gate current. This reduces the amplification factor. By these reasons, gain falls at the high frequency region.

Mid frequency region: The voltage gain in this region remains constant. The coupling capacitors offer zero reactance above the lower cut-off frequency, and at the same time shunt capacitors offer very high and almost constant reactance independent of frequency up to upper cut-off frequency. So in this frequency region gain remains maximum and constant.

The frequencies where the gain is 70.7% of the maximum gain are called cutoff frequencies. There are two such frequencies  $f_1$  and  $f_2$  one on the lower frequency side and the other on the higher frequency side.

Bandwidth  $=(f_2-f_1)$ . On decibel scale the power reduction is of three decibels.

#### **Procedure**:

# Plotting frequency response curve:

Circuit should be connected as shown in the figure. 30mV (peak to peak) is applied to the gate source using signal generator. Now measure the output voltage by varying the frequency from 50Hz to 1MHz. First the output voltage increases and reaches a constant value. It remains constant up to a certain frequency and then it decreases. Measure the input and out put voltages in the range 50 Hz to 2Mhz and calculate the gain in dB. After completion of taking readings draw graph taking log f on x axis and gain on Y axis. It is called frequency response curve.

#### Measuring the input and output resistances:

Connect the circuit as shown in fig. Measure the generator voltage and voltage across  $R_s$  as  $R_s$  is varied from zero in steps of 100 ohms the voltage across it increases. Note the value of Rs at which  $V_i$  is equal to  $V_s/2$ . At this value  $R_i = R_s$

For output resistance put decade box at output and vary that until it comes to  $V_o/2$ . It is the output resistance  $R_o$ .

# **Observations:**

| FREQUENCY | OUTPUT<br>VOLTAGE<br>(Vo) volts | Gain<br>Vo/Vi | Gain dB<br>20 log<br>(Vo/Vi) |

|-----------|---------------------------------|---------------|------------------------------|

|           |                                 |               |                              |

**Precautions:**1.the coarse and fine knobs of a power supply should be kept in the minimum position before the commencement of the experiment.

- 2.Loose connections are to be avoided.

- 3.Readings must be take carefully on C.R.O.

- 4. At each observations the input voltage magnitude maintain at 30mv peak to peak.

## Result:

Band Width obtained from the graph = kHz.

Input resistance Ri = k Ohms.

Output resistance Ro = k Ohms.

#### **Experiment No:4**

#### **ASTABLE MULTI VIBRATOR USING 741**

1

AIM:- To construct an astable multi vibrator with 741 op amp and generate different frequencies with different time constants and compare them with calculated values .

APPARATUS;- IC 741, power supply, signal generator, CRO, resistances and capacitances of various values.

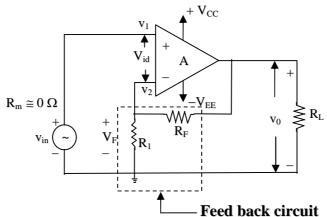

#### THEORY:-

#### **Square Wave Generator:**

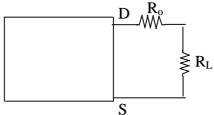

In contrast to sine wave oscillator, square wave outputs are generated when the op-amp is forced to operate in the saturated regions, that is, the output of the op-amp is forced to swing repetitively between positive saturation +  $V_{sat}(\cong + V_{CC})$  and negative saturation- $V_{sat}(\cong - V_{EE})$ , resulting in the square wave output. Such a circuit shown in fig.

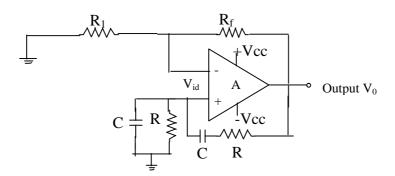

Fig (a) Square wave generator (b) Wave form of output voltage.  $v_0$  and capacitor voltage  $v_2$  of the square wave generator.

This square wave generator is also called a free-running multi-vibrator. Assume that the voltage across the capacitor C is zero volts at the instant the dc supply voltages  $+V_{CC}$  and  $-V_{EE}$  are applied. This means that the voltage at the inverting terminal is zero initially. At the same instant, however, the voltage  $V_1$  at the non-inverting terminal is very small finite value, that is a function of the output offset voltage  $V_{001}$  and the values of  $R_1$  and  $R_2$  resistors. Thus the differential input voltage  $V_{id}$  is equal to the voltage  $V_1$  at the non-inverting terminal. Although very small, voltage  $V_1$  will start to drive the op-amp into saturation.

M.Sc. Physics 2 Astable Multivibrator

For example, suppose that the output offset voltage  $V_{001}$  is positive and that, therefore voltage  $V_1$  is also positive. Since initially the capacitor C acts as a short circuit, the gain of the amplifier is very large (A); hence  $V_1$  drives the output of the op-amp to its positive saturation +  $V_{sat}$  with the output voltage of the op-amp as + $V_{sat}$ , the capacitor  $C_2$  starts charging toward + $V_{sat}$  through the resistor, R. However, as soon as the voltage  $v_2$  across the capacitor is slightly more positive than  $V_1$ , the output of op-amp is forced to switch to a negative saturation, - $V_{sat}$ . With the op-amps output voltage as negative saturation, - $V_{sat}$  the voltage  $V_1$  across  $R_1$  is also negative, since  $V_1$  =

$$\frac{R_1}{R_1 + R_2} (-V_{sat})$$

----- (1)

Thus the net differential voltage  $V_{id} = V_1 - V_2$  is negative, which holds the output of the opamp in negative saturation. The output remains in negative saturation until the capacitor C discharges and then recharges to a negative voltage slightly higher than the  $-V_1$  [see Fig.] Now, as soon as the capacitor voltage  $v_2$  becomes more negative than  $-V_1$ , the net differential voltage  $V_{id}$  becomes positive and hence drives the output of the op-amp back to its positive saturation  $+V_{sat}$ . This completes one cycle. With output at  $+V_{sar}$ , and voltage  $V_1$ , at the non-inverting input is

$$V_1 = \frac{R_1}{R_1 + R} (+V_{sat})$$

-----(2)

The time period T of the output waveform is given by

$$T = 2RC \ln \left( \frac{2R_1 + R_2}{R_2} \right) \quad ---- \quad (3)$$

Equation 3 indicates that the frequency of the output  $f_0$  is not only a function of the RC time constant but also of the relationship between  $R_1$  and  $R_2$ . For example If  $R_2 = 1.16 R_1$ , equation 3 becomes

$$f_0 = \frac{1}{2RC}$$

---- (4)

Equation (4) shows that the smaller the RC time constant, the higher the output frequency  $f_0$  and vice versa. As in the sine wave oscillator, the highest frequency square wave generated is also set by the slew rate of the op-amp. In practice, each inverting and non-inverting terminal needs a series resistor  $R_s$  to prevent excessive differential current flow because the input of the op-amp is subjected to large differential voltage.  $R_s$  should have a value of 100 K $\Omega$  or higher.

The feed back resistance R and the capacitance C provides the integrator action . The op-amp serves as a regenerative comparator . The output of comparator is limited by the saturation level of the op-amp . A function  $\beta=R_1/R_1+R_2$  of the output voltage is feed back to the comparator that compares the voltage across the capacitor with the voltage and switches to negative saturation limit .

3

The moment  $V_I$  becomes greater than  $\beta V_e$ , the capacitor begins to discharge through  $R_b$  until  $V_c$  is equal to  $\beta V_0$ . The output is than switched on to the +ve saturations. The momentj v  $V_c$  becomes less than  $BV_0$ .

PROCEDURE: The circuit is connected as shown in fig and the output wave form is observed using the CRO. The capacitor is varied and the frequency is measured at each step, The observed frequencies are compared with the calculated ones.

#### **OBSERVATIONS:**

DC supply voltage  $V_{cc} = .....V$

| $R_1$ | $R_2=1.16R_1$ | Capacitance C(µf) | Time period | Frequency  |            |

|-------|---------------|-------------------|-------------|------------|------------|

|       |               |                   |             | (Observed) | Calculated |

|       |               |                   |             |            |            |

|       |               |                   |             |            |            |

|       |               |                   |             |            |            |

#### **PRECAUTIONS:**

- 1. Distortion should not be in the waves.

- 2. Connections must be properly verified.

- 3. Power supply should be adjusted to 15V or less.

#### **RESULT:**

The calculated frequencies are found to be in good agreement with the observed values

Experiment:4

# Astable multi-vibrator using 555

1

**Aim:** To form an astable multivibrator and study its wave forms.

**Apparatus :** 555 timer IC,0-15 V DC power supply, capacitors, resistors, connecting Wires and bread board.

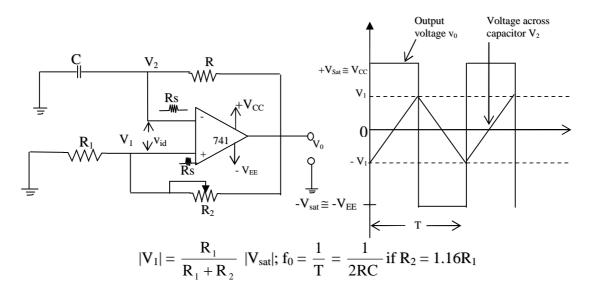

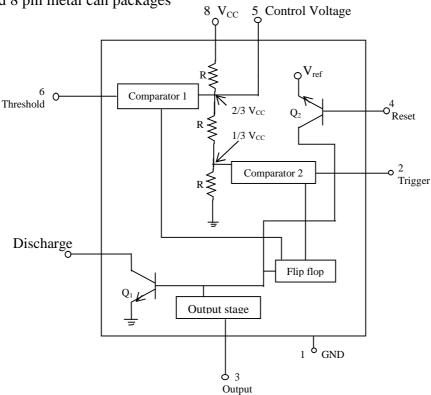

#### **Description of 555 timer:**

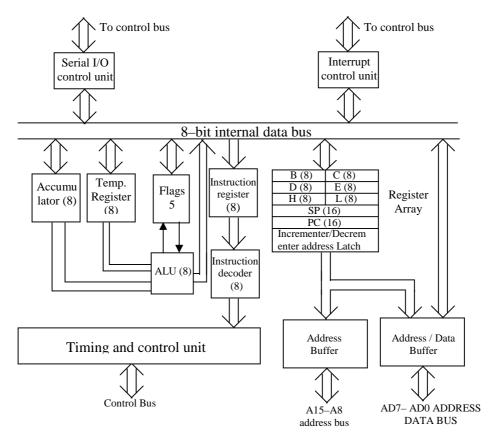

The 555 Timer and its pin configurations: Signetic corporation introduced this device as the SE / NE555 in early 1970 for the first time. It is one of the most versatile linear integrated circuit. The applications of 555 timer includes mono-stable and a stable multi-vibrators, a.c-d.c converters, digital logic probes, wave form generators, analog frequency meters and tachometers, temperature measurement and control, infrared transmitters, burglar or toxic gas alarm, voltage regulators, electronic eyes and many others. The 555 is a monolithic timing circuit that can produce accurate and highly stable time delays or oscillation. In other words the timer basically operates in one of the two modes: either as a mono stable multi-vibrator (one shot) or as an astable (free running) multi-vibrator. The device is available as an 8 pin metal, as an 8-pin mini DIP or a 14-pin DIP. Fig shows that the pin connection diagram and the block diagram of the SE/NE 555 timer. The SE 555 is designed for the operating temperature range of -55 to  $+125^{\circ}$ c, while NE 555 operates over a temperature range of 0 to  $+70^{\circ}$ c. The important features of the 555 Timer are (1) It operates on +5 to +15v supply voltage in both free running (astable) and one shot (mono stable) modes; (2) It has an adjustable duty cycle; timing is from micro seconds through hours; (3) It has high current output; it can source or sink 200 mA; (4) The output can drive TTL and has a temperature stability of 50 parts per million (ppm) per degree Celsius change in temperature.

Fig (1a) 555 timer connecting diagram

Before proceeding with the operations of 555 Timer an astable multi-vibrator, it is important to examine its pin functions. The pin number is used in the following discussion refer to the 8 pin mini DIP and 8 pin metal can packages

Fig (1b) block diagram

**Pin 1:** Ground. All voltages are measured w.r.t. this terminal.

**Pin 2:** trigger. The output of the timer depends on the amplitude of the external trigger pulse applied to this pin. The output is low if the voltage at this pin is greater than 2/3 V<sub>cc</sub>. However, when a negative going pulse of amplitude larger than 1/3 V<sub>cc</sub> applied to this pin, the comparator 2 output goes low, which is turn switches the output of the timer high. The output remains high as long as the trigger terminal is held at a low voltage.

**Pin 3:** there are two ways a load can be connected to the output terminal: either between pin 3 and ground (pin 1) or between pin 3 and supply voltage  $+V_{cc}$  (pin 8). When the output is low, the load current flows through the load connected between 3 and  $+V_{cc}$  into the output terminal and is called the sink current. However, the current through the grounded load is zero when the output is low. For this reason, the load connected between 3 and  $+V_{cc}$  is called normally on load, and that

connected between pin 3 and ground normally off load and that connected between pin 3 and ground is called the normally off load.

**Pin 4:** Reset. The 555 timer can be reset (disabled) by applying a negative pulse to this pin. When the reset function is not in use, the reset terminal should be connected to  $+V_{cc}$  to avoid any possibility of false triggering.

**Pin 5:** control voltage. An external voltage applied to this terminal changes the threshold as well as the trigger voltage. In other words, by imposing a voltage on this pin or by connecting a pot between this pin and ground, the pulse width of the waveform can be varied. When not used, the control pin should be bypassed to ground with a 0.01μF capacitor to prevent noise problems.

**Pin 6:** Threshold. This is the non-inverting input terminal of comparator 1, which monitors the voltage across the external capacitor. When the voltage at this point is  $\geq$  threshold voltage  $\frac{2}{3}V_{cc}$ , the output of comparator 1 goes high, which in turn switches the output of the timer low.

**Pin 7:** Discharge. This pin is connected internally to the collector of transistor  $Q_1$ . When the output is high,  $Q_1$  is off and acts as an open circuit to the external capacitor C connected across it. On the other hand, when the output is low,  $Q_1$  is saturated and acts as a short circuit, shorting out the external capacitor C to ground

**Pin 8:**  $+V_{cc}$ . The supply voltage of +5V to +18V is applied to this pin with respect to ground (pin 1)

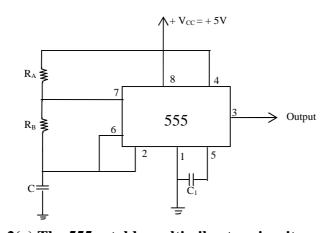

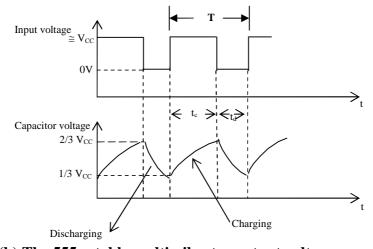

# The 555 as an astable multi-vibrator:

An astable multi-vibrator, often called a free running multi-vibrator, is a rectangular wave generating circuit. The time during which output is either high or low is determined by the two resistors and a capacitor, which are externally connected to the timer 555

<u>Astable operation:</u> Fig 2(a) shows the 555 timer connected as an astable multi-vibrator. Initially, when the output is high, capacitor C starts charging toward  $V_{cc}$  through  $R_A$  and  $R_B$ .

M.Sc. Physics 4 Astable multivibrator

However as soon as voltage across the capacitor equals  $\frac{2}{3}V_{cc}$ , comparator 1 triggers the flip-flop, and the output switches low [see fig 2(b)]. Now capacitor C starts discharging through  $R_B$  and transistor. When the voltage across C equals  $\frac{1}{3}V_{cc}$ , comparator 2's output triggers the flip-flop and the output goes high. Then the cycle repeats. The output voltage and capacitor voltage waveforms are shown in figure 2(b).

As shown in this figure, the capacitor C is periodically charged and discharged between  $\frac{2}{3}$   $V_{cc}$  and  $\frac{1}{3}$   $V_{cc}$  respectively. The time during which the capacitor charges from  $\frac{1}{3}$   $V_{cc}$  to  $\frac{2}{3}$   $V_{cc}$  is equal to the time the output is high and is given by

$$t_c = 0.69 (R_A + R_B)C$$

----- (1)

Fig 2(a) The 555 astable multi-vibrator circuit

Fig 2(b) The 555 astable multi-vibrator output voltage wave form and voltage across the capacitor.

Where  $R_A$  and  $R_B$  are is ohms and C is in Farads. Similarly the time during which the capacitor discharges from  $\frac{2}{3} V_{cc}$  to  $\frac{1}{3} V_{cc}$  is equal to the time, the output is low and is given by

$$t_d = 0.69 R_B C$$

-----(2)

Thus the total time period of the output waveforms is

$$T = t_c + t_d = 0.69 (R_A + 2R_B) C$$

-----(3)

This, in turn gives the frequency of oscillation as

$$f_0 = \frac{1}{T} = \frac{1.45}{(R_A + 2R_B)C}$$

----- (4)

Equation (4) indicates then the frequency  $f_0$  is independent of the supply voltage  $V_{cc}$ .

Output is a square wave of period  $t = 0.68(R_1 + R_2)C$ .  $T_2 = 0.698R_2C$ :

$$T = T_1 + T_2$$

$$T = 0.68(R_1 + 2R_2)C.$$

$$R = 1/T = 1.443/(R_1 + 2R_2)C$$

PROCEDURE: The circuit is connected using capacitors and the output waveform is observed using the CRO.  $R_1$  and  $R_2$  are chosen 1K and 20K respectively. The supply voltage is given to the fourth and eighth pins respectively. The capacitor is varied and the frequency is measured at each step. The observed frequency is compared with the calculated values. For each combination of R & C the peak value of the output voltage and the voltage across sixth pin are measured. For each setting using a tracing paper the waveform observed on CRO screen is traced. The effect of change in the value are recorded, by varying  $R_1$  the effect of it on the waveform is studied.

| M.Sc. Physics | 6 | Astable multivibrator |

|---------------|---|-----------------------|

|---------------|---|-----------------------|

# **Observations:**

DC supply voltage  $V_{cc} = \dots V$

| $R_A$ | $R_{\rm B}$ | Capacitance C (µf) | Time period | Frequency  |            |

|-------|-------------|--------------------|-------------|------------|------------|

|       |             |                    |             | (Observed) | Calculated |

|       |             |                    |             |            |            |

|       |             |                    |             |            |            |

|       |             |                    |             |            |            |

|       |             |                    |             |            |            |

|       |             |                    |             |            |            |

|       |             |                    |             |            |            |

# PRECAUTIONS:

- 1. Distortion should not be in the waves.

- 2. Connections must be properly verified.

- 3. Power supply should be adjusted to 15V or less.

# **RESULT:**

The calculated frequencies are found to be good agreement with the observed values.

#### Experiment No. 5

#### INVERTING, NONINVERTING and SUMMING AMPLIFIER

1

AIM:- To study the working of op-Amp as Inverting, Non-inverting and Summing amplifiers.

#### APPARATUS:-

| S.NO. | NAME OF THE ITEM        | RANGE                               | QUANTITY |

|-------|-------------------------|-------------------------------------|----------|

| 1.    | DC Regulated Power Supp | oly ±12V                            | 1        |

| 2.    | Digital multi meter     | _                                   | 1        |

| 3     | breadboard              | -                                   | 1        |

| 4.    | Op-Amp IC-741           |                                     | 1        |

| 5.    | Resistances             | $10$ k $\Omega$                     | 3        |

|       | 1                       | $k\Omega$ ,2.2 $k\Omega$            |          |

|       | 3                       | $3.3$ k $\Omega$ , $4.7$ k $\Omega$ | 1        |

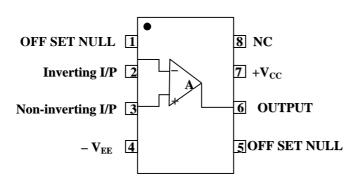

#### Details of 741 OP AMP:

IC 741 is available in two packages. The pin configuration of 741 op-amp in dual in line package (DIP) is given below

It is the most commonly and widely used general-purpose op-amp. It has an integrated 30pF MOS capacitor. It has high input impedance (>  $1M\Omega$ ), low output impedance (750  $\Omega$ ) and large voltage gain (200,000).

Fig (1.9) pin configuration of  $\mu$ A-741 op-amp

A dot on the top left corner is used to identify pin number 1. It needs a  $\pm 12V$  DC dual power supply. It is basically a high gain differential amplifier with two inputs.

#### Operational Amplifier:

An operational amplifier is a direct-coupled high gain amplifier usually consists of one or more differential amplifiers and usually followed by a level translator and an output stage. The output

stage is generally a push pull or push pull complementary symmetry pair. An operational amplifier is available as a single integrated circuit package. The operational amplifier is a versatile device that can be used to amplify dc as well as ac input signals and was originally designed for computing such mathematical functions as addition, subtraction, multiplication and integration. Thus the name operational amplifier stems from its original use for doing these

mathematical operations and so is abbreviated to op-amp. With the addition of suitable external feed back component the modern day operational amplifier can be used for a variety of applications. Such as ac and dc signal amplification, active filters, oscillators, comparators, regulators and others.

# **Schematic symbol:**

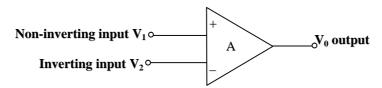

The most widely used symbol for a circuit with two inputs and one out put is shown in fig (1.6)

In fig (1.6) Fig (1.6) Schematic symbol of op-amp

$v_1$  = voltage at the non-inverting input (volts)

$v_2$  = voltage at the inverting input (volts)

$v_o$  = output voltage (voltage)

All these are measured w.r.t. ground

A = large signal voltage gain that is specified on the data sheets for an op-amp

power supply and other pin connections are not usually shown in circuits. Since the input differential amplifier stage of the op-amp is designed to be operated in the differential mode, the differential inputs are designated by the (+) and (-) notations, the (+) input is used for non-inverting input. An ac signal (or dc voltage) applied to this input produces an in-phase (or same polarity) signal at the output. On the other hand the (-) input is the inverting input because an ac signal (or dc voltage) applied to this input produces an 180 out of phase (or opposite polarity) signal at the output

#### **Ideal op-amp:**

An ideal op-amp exhibits the following electrical characteristics.

- (1) Infinite voltage gain A<sub>V</sub>.

- (2) Infinite input resistance R<sub>i</sub>, so that, almost any signal source can drive it and there is no loading of the preceding stage.

3

- (3) Zero output resistance R<sub>o</sub>, so that, output can drive an infinite number of other devices

- (4) Zero output voltage when the input voltage is zero.

- (5) Infinite bandwidth, so that, any frequency signal from 0 to ∝ Hz can be amplified with out attenuation.

- (6) Infinite common mode rejection ratio so that output common mode noise voltage is zero.

- (7) Infinite slew rate so that voltage changes occur simultaneously with input voltage changes.

There are practical op-amps that can be made to achieve some of these characteristic using a negative feedback arrangement. In particular, the input resistance, the output resistance, and bandwidth can be brought close to ideal values by this method.

As the open loop gain of op-amp is very high, only very small signals (of the order of micro-volts or less) having very low frequency may be amplified accurately with out distortion. However, signals this small are very susceptible to noise. Besides being large the open loop gain of the op-amp is not constant. The voltage gain varies with changes in temperature and power supply as well as with mass production techniques. The variations in voltage gain are relatively large in open-loop op-amp, in particular, which makes the open-loop op-amp unsuitable for many linear applications. In most linear applications the output is proportional to the input and is of the same type.

Further the bandwidth (band of frequencies for which the gain remains constant) of most open-loop op-amps is negligibly small - almost a zero. For this reason, the open-loop op-amp is impractical in ac applications. For instance the open loop bandwidth of the 741C is approximately 5Hz. However, in almost all ac applications a bandwidth larger than 5 Hz is needed.

Because of the above stated reasons, the open loop op-amp is generally not used in linear applications. Never the less in certain applications the open-loop op-amp is purposely used as a nonlinear device; that is a square ware output is obtained by deliberately applying a relatively large input signal. Open-loop op-amp configurations are most suitable in such applications.

We will be able to select as well as control the gain of the op-amp, if we introduce a modification in the basic circuit. This modification involves the use of feedback, that is, an output signal is fed back to the input either directly or via another network. If the signal fed back is of opposite polarity or out of phase by 180° with respect to input signal, the feedback is called of negative feedback. An amplifier with negative feedback has a self - correcting ability against any change in output voltage caused by changes in environmental conditions. Negative feedback is also known as degenerative feedback because when used it degenerates (reduces) the output voltage amplitude and in turn reduces the output gain.

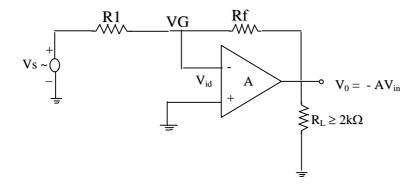

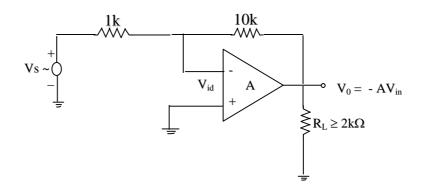

# The inverting amplifier with negative feed back:

In the inverting amplifier only one input is applied and that, to the inverting input terminal. The non-inverting input terminal is grounded. Since  $v_1 = 0$  and  $v_2 = v_{in}$ .

Fig 1.13 Inverting amplifier

The negative sign indicates that the output voltage is out of phase with respect to input by  $180^{0}$  or is of opposite polarity. Thus in the inverting amplifier the input signal is amplified by gain A and is also inverted at the output.

Gain of inverting amplifier with feed back:

As the non inverting input of the amplifier is grounded and as no current passes through the input resistance (it is assumed to be infinite in ideal case)

The inverting input terminal also must be at zero potential as there cannot be any voltage drop across  $R_i$ . The junction point of  $R_1$ ,  $R_f$  and inverting input is called virtual ground. Therefore

5

the input current

$$I_i = \frac{V_s}{R_1}$$

flows through Rf resulting in a voltage drop =  $R_f * I_i = -V_o$ .

Therefore

$$V_o = R_f x (-V_s / R_1) = -(R_f / R_1) x v_s$$

Voltage gain Av =

$$V_o/V_i$$

= -  $(R_f/R_1)$

The expression for voltage gain doesn't contain any parameter pertaining to

OP AMP. If  $R_f = R_1$ . The input and output signals have equal amplitude but differ in phase by  $180^{\circ}$ . It is called inverting unity gain amplifier. If the ratio  $R_f/R_1$  is varied the output signal amplitude can be scaled up or down. In this application it is called scale changer. Because of virtual ground mentioned above any signal connected to the inverting input through a resistance  $R_x = R_1$  supplies current independent of other sources. The current flowing through  $R_f$  is algebraic sum of the currents entering in the node. As a result the output voltage can be considered as sum of input signal amplitudes. In this configuration such an amplifier is called summing amplifier. Any number of input signals can be connected like this and the output voltage of the summing amplifier is

$$v_o = -\frac{R_f}{R}(v_1 + v_2 + ...v_x + ...v_n)$$

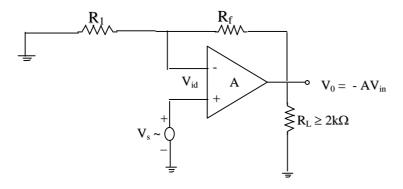

#### The non-inverting amplifier:

Fig 2 Non - Inverting amplifier

Fig 2 shows the open loop configuration of non inverting amplifier. In this configuration the input is applied to the non inverting input terminal and the inverting input terminal is grounded.

In the circuit shown below  $v_1=v_{in}$  and  $v_2=0v$ . Therefore according to equation  $v_0=Av_{in}$ . This means that the output voltage is A times larger than the input voltage and is in phase with input signal. The type of feedback involved is called voltage series feedback. The circuit 2 is redrawn to show feedback.

Fig (2.2): voltage series feed back amplifier.

Expression for voltage gain:

As the input resistance of the amplifier is infinite, the inverting terminal will be at same potential as that of non inverting input. The current flowing through the resistance  $R_f$  is  $(v_o-v_1)/R_f$ . It must be equal to  $v_1/R_1$  in magnitude. Equating

$$\frac{v_1}{R_1} = -\frac{(v_1 - v_o)}{R_f}$$

we can rewrite it as

$$v_1(\frac{1}{R_f} + \frac{1}{R_1}) = \frac{v_o}{R_f}$$

The voltage gain

$$A_v = \frac{v_o}{v_s} = 1 + \frac{R_f}{R_1}$$

In this configuration output signal will be in phase with input. For  $R_1=R_f$  the gain is 2.

#### PROCEDURE:-

# **INVERTING AMPLIFIER:-**

- 1. Select  $R_f$  and  $R_1$  depending on the gain required. Connections are made as per the circuit diagram . Use low wattage resistors preferably one eighth watt so that resistance leads smoothly fit into the breadboard. When high wattage resistors are used in a circuit do not use them in bread board. Use separate group board for them.

- 2. Fix the IC741 on breadboard such that pins insert in the holes without bending. Enough care must be taken while inserting and removing ICs from bread boards and sockets. Better use IC inserters and pluckers for this.

- 3. Use minimum length of wire to make connections. The gauge of the wire is selected such that it goes into the whole smoothly. Bent wires should not be inserted. Use a wire cutter cum sleeve remover to cut bent ends and to remove plastic sleeve. Use various colours of wires so that the connections can be identified easily. Use common ground. If several ground points are used ensure that they are all common by checking resistance between those points.

- 4. Use fixed voltage DC power supply preferably SMPs. The +12 V DC line is given to pin No. 7. −12V DC is given to pin No. 5. Fix the

- 2. For inverting amplifier vary the input voltage from 1 to 6v in steps of 1v and measure the output voltage as a function of the input voltage.

- 3. Compare the experimental gain with the total gain of -R<sub>F</sub>/R<sub>1</sub>

| S.No. | $R_1$ | Output Voltage |             | Gain      |             |

|-------|-------|----------------|-------------|-----------|-------------|

|       |       | Practical      | Theoretical | Practical | Theoretical |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

# **SUMMING AMPLIFIER:-**

- 1. Apply  $V_1$  and  $vary V_2$  from .5 to 2.5v in steps of .5 measure the output voltage with the help of multimeter.

- 2. Compare the experimental values with the theoretical values.

| S.No | Input voltage |       | Outpu       | Output voltage |  |

|------|---------------|-------|-------------|----------------|--|

|      | $V_1$         | $V_2$ | Theoretical | Practical      |  |

|      |               |       |             |                |  |

|      |               |       |             |                |  |

|      |               |       |             |                |  |

|      |               |       |             |                |  |

| M.Sc. Physics 8 | Experiment No. 5 |

|-----------------|------------------|

|-----------------|------------------|

# NONINVERTING AMPLIFIER:-

1.Apply the input voltage to the non-inverting terminal from 0.5 to 2.5 in steps of 0.5V measure the output

voltages.

2. Compare the practical and theoretical values.

| S.No. | $R_1$ | Output Voltage |             | Ga        | nin         |

|-------|-------|----------------|-------------|-----------|-------------|

|       |       | Practical      | Theoretical | Practical | Theoretical |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

|       |       |                |             |           |             |

# PRECAUTIONS:

- 1) Check the IC for corking by using it in inverting amplifier.

- 2) Ensure common ground for all ground connections.

- 3) Some function generators may have offset null facility. Use it if no output signal is observed even after circuit is assembled properly.

# **RESULT:-**

We observed that the OP-AMP is used as an inverting ,non-inverting and summing amplifiers.

Experiment No.6

# WEIN BRIDGE OSCILLATOR

**AIM**: To construct wean bridge oscillator using IC 741 and to generate sine wave of different frequencies.

**APPARATUS**: op-amp IC 741, resistance 1 kohm-2, 100 kohm, 10kohm, potentiometer 10k ohm pot, capacitors 0.003Mf, 0.22mf, 0.002mf, breadboard, DC regulated power supply, function generator, dual trace C.R.O, connecting wires.

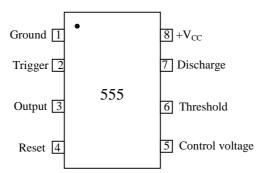

Fig 1 Wein's bridge oscillator

**THEORY:** An oscillator in which a balanced Wein's bridge is used as the feedback network is called the Wein's bridge oscillator. The active element is an operational amplifier which has a very large positive gain negligible output resistance and very high input resistance. At  $W_0$  frequency, the network introduces zero phase shift. At this frequency the feedback ratio is 1/3. that is it introduces attenuation of 1/3. To maintain oscillations the gain must be unity. This is achieved by introducing negative feedback through R1 and Rf. The values of  $R_1$  and  $R_f$  are adjusted such that  $R_1 = 2R_f$ .

The cuircuit oscillates as long as =1/3. Any deviation from this condition makes the oscillator unstable. The amplitude of the oscillator may be stabilized by varying negative feedback by using a potentiometer in place of  $R_1$ . If for any reason, the amplitude of the output voltage increases, the amount of negative feedback increases, there by bringing down the amplitude to a suitable value.

# PROCEDURE:

- 1) connect the circuit as shown in diagram.

- 2) choose R<sub>1</sub>=10kohm potentiometer for R<sub>f</sub> connected as variable resistance.

- 3) Variation of potentiometer allows one to start the oscillations and also to control the distortion.

- 4) Adjust the potentiomrer such that the oscillations are stable and distortion is minimum.

- 5) directly read the frequency of the sine wave in C.R.O.

- 6) by varying the capacitance value repeat the calibration.

- 7) repeat the same procedure for different capacitance values.

#### **Table**

| S.No | Capacitance | Time period (T) = | Observed frequency (1/T) | Calculated |

|------|-------------|-------------------|--------------------------|------------|

|      | μf          | λ t Seconds       | Hz                       | frequency  |

|      |             |                   |                          | 1/2πRC Hz  |

|      |             |                   |                          |            |

|      |             |                   |                          |            |

|      |             |                   |                          |            |

|      |             |                   |                          |            |

|      |             |                   |                          |            |

|      |             |                   |                          |            |

|      |             |                   |                          |            |

#### **PRECAUTIONS:**

- 1) bread board should be cheeked before giving the connections.

- 2) it is checked with millimeter.

- 3) IC 741 also be checked by gain checking circuit as shown in the figure.

- 4) Loose connections are avoided in the circuit.

- 5) The conducting parts of any two wires cannot touch each other.

- 6) The C.R.O reading should be taken carefully.

#### **RESULT:**

Wien bridge oscillator using OP-AMP IC 741 was constructed and sine wave was generated for different frequencies by changing the capacitors for a given value of R.

Experiment is also repeated for different values of R keeping a fixed value for C. The calculated and observed frequencies are agreeing satisfactorily.

Suggestions to teachers: The students may be asked to trace the waveforms for different values of R and C maintaining RC product at a constant value and record their remarks.

Experiment No.7

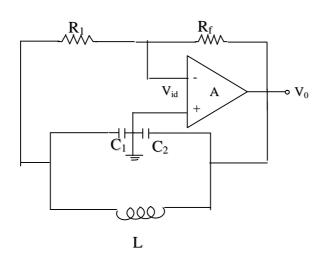

# Colpitts oscillator

1

AIM: To construct a Colpitts oscillator using Op amp IC 741 and to study its performance for different inductance (L) values and capacitance values.

**APPARATUS**: Op-amp IC 741, resistance 1 kohm-2, 100 kohm, 10kohm, capacitors 0.003Mf, 0.22mf, 0.022mf, 0.002mf each 2 nos, breadboard, DC regulated power supply(12V DC), function generator, dual trace C.R.O, bread board, single strand connecting wires of different colors variable inductance box.

# Theory:

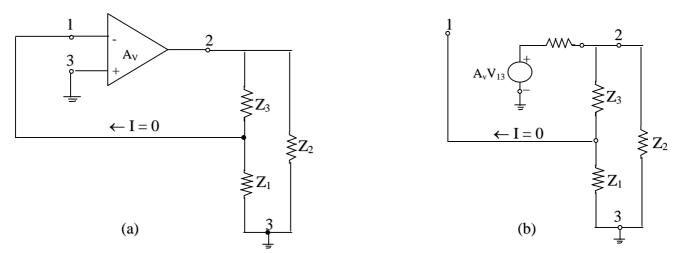

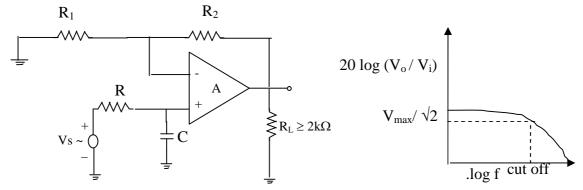

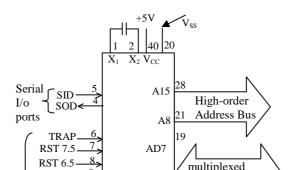

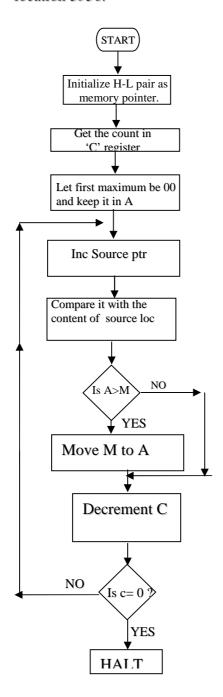

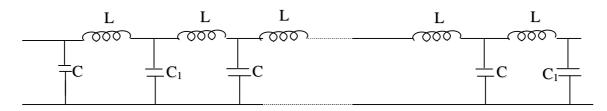

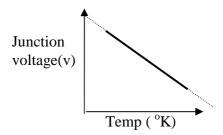

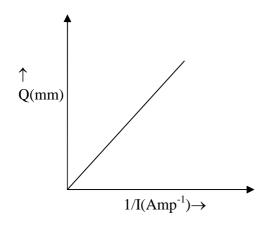

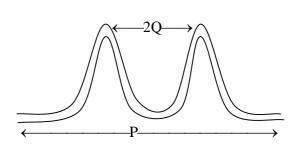

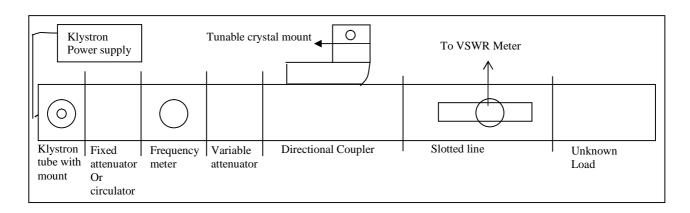

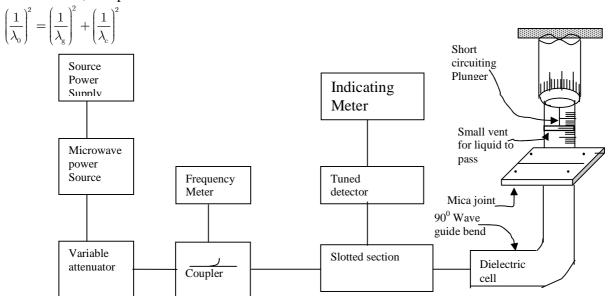

Fig 1(a) The basic configuration for many resonant-circuit oscillators (b) The linear equivalent circuit using an operational amplifier